2022年4月自考数字系统设计与PLD应用技术真题试卷出来了,免费下载哦,欢迎有需要的同学下载学习哦,此外还包含2022年4月高等教育自学考试全国统一命题考试真题试卷免费下载。

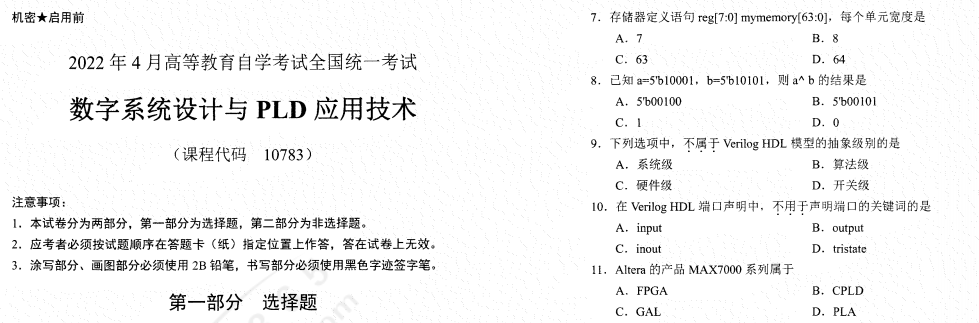

机密★启用前

2022年4月高等教育自学考试全国统一考试数字系统设计与PLD应用技术

课程代码:10783

注意事项

- 本试卷分为两部分,第一部分为选择题,第二部分为非选择题。

- 应考者必须按试题顺序在答题卡(纸)指定位置上作答,答在试卷上无效”

- 涂写部分、画图部分必须使用2B铅笔,书写部分必须使用黑色字迹签字笔。

点击免费下载:2022年4月高等教育自学考试全国统一命题考试

第一部分选择题

一、单项选择题:本大题共15小题,每小题1分,共15分。在每小题列出的备选项中 只有一项是最符合题目要求的,请将其选出。.

- 下列选项中,不層于IP核的类型的是

A.软核 B.砲核

C.微处理器核 D.固核

- 绝大多数FPGA器件都是基于下列哪种结构卖氟

A.乘积项 B.查找表

:C. ROM 「D/ 与或阵列””

己知 a=5’b 10001, b=5’bl0101,则 a、b 的结果是

- 5^00100

- 5W0101

- 1 D. 0

下列选项中,不層于Verilog HDL模型的抽象级别的是

A.系统级 B.算法级

C.硬件级 D.开关级

在Verilog HDL端口声明中,不用于声明端口的关键词的是

- input B.

- inout D.

Altera的产品MAX7000系列属于

- FPGAGAL D.

Quartus II的设计工程不謂擊设定、

A.工作目录 B.

output tristate

CPLD

PLA

添加设计文件

C.目标器律: D.编程下载”

已知 c=l’bl, 3=41,1001, b=4’b0100,若 d=(c)?a:b,则 d 的值为

- 4’bl001 B. 4’b0100

- 1 D. 0

已知 a=5%11001, b=5’bl0101, M a&&b 的结果是

- 5*b 10001

5^10101

| A.机器语言 | B.汇编语言’ |

| C,高级语言 | D. C语言: |

| 4,关键字posedge表示 | |

| A.上升沿 | B.下降沿 |

| C. 0 | D. 1 |

| 5.下列标识符哪个是不正确的 | |

| A. adder 1 | B. sub_ |

| C. mux21 | D. 1 decode |

Verilog HDL是在下列哪种语言的基础上发展起来的

15,

- 1 D.

若a=5’b 11011,则a«2的结果是

- 5’bllOH

- 5’bOOllO

B.

D.

51)01100

6.下列选项中,T Verilog HDL中的逻辑状态的是

- 0 B. 1

C.低阻 D.高阻

数字系统设计与PLD应用技术试题 第1页(共4页)

二、多项选择题:本大题共5小题,每小题2分,共10分。在每小题列岀的备选项中 至少有两项是符合题目要求的,请将其选岀,错选、多选或少选均无分。

16.硬件描述语言进行电路设计的突出优点有

便于复用和交流 B.设计与工艺无关

方便保存和修改:* D.适合大规模电

| A.模块声明 | B.端口定义 |

| C.结构体描述 | D.信号类型声明 |

| E.逻辑功能描述 | |

| 任务和函数的区别有 | |

| A.任务只可在过程语句调用 | B.函数可以作为表达式中的一个操作数 |

| C.任务可以调用函数 | D.函数可以调用任务 |

| E.任务没有返回值 | |

| Verilog HDL中的变量可分为的数据类型有 | |

| A. net | B ・ double |

| C. float | D. variable |

| E. char | |

| 下列Verilog标识符中,合法的标识符有 | |

| A. cl_bl | B. aluS |

| C・ b3_* | D. ladder |

| E. mux | |

Verilog HDL程序包括

第二部分非选择题

三、程序填空题:本大题共2小题,每小题5分,共10分。

21.按要求完成计数器程序填空。

module Johnson(clk?clr,qout);

| ① | 〃声明elk,clr为输入 |

| output reg[3:0] qout; | |

| always仞(② | )〃列岀敏感信号 |

| begin if (clr) ③ | [ 〃计数器清零 |

| else begin ④ | 〃左移一位 |

| ⑤ | ,//最高位取反,然后赋值给最低位 |

| end end | |

| endmodule |

- ;〃声明out为输出

always @(in0 or ini or in2 or in3 or sei) case(sel)

WO : out=in0;

- ; 〃选中ini到输出

1)10 : out=in2;

1,11 : out=in3;

- ; 〃缺省项,输岀为未知电平

- // case语句结束

endmodule

四、 名词解释题:本大题共5小题,每小题3分,共15分。

- CPLD

- ASIC

- JTAG

- EDA

- Synthesis

五、 简答题:本大题共4小题,每小题5分,共20分。

- 功能仿真和时序仿真有什么差别?

- 过程赋值语句有哪两种方式,各有什么特点?

- 简述基于FPGA的数字系统设计流程。

- FPGA和CPLD在结构上有什么明显区别,各有什么特点?

六、 程序设计:本大题共3小题,每小题10分,共30分。

- 设计一个1位全加器。

- 用函数定义一个8-3优先编码器。

- 设计实现一个简单微处理器,根据输入的指令,能实现四种操作,分别为两数相加, 两数相减,操作数加1、操作数减1。操作码和操作数均从输入指令中提取。操作 指令一共18位,最高两位为操作码,低8位是第一个操作数,中间8位为第二个 操作数。

- 4选1数据选择器程序如下,完成填空。

module mux41(out,in0,inl,in2,in3,sel);

- ; 〃声明in0,ml,in2,in3 为输入

input[l:0] sei;

点击免费下载:2022年4月高等教育自学考试全国统一命题考试

以上就是2022年4月自考数字系统设计与PLD应用技术真题试卷,有需要的同学可以自行下载使用,有什么问题可以随时留言咨询。

中国自考网:建议开通SVIP超级会员更划算,全站所有资源永久免费下载(正版自考网课除外)

1. 本站所有网课课程资料来源于用户上传和网络收集,如有侵权请邮件联系站长!

2. 分享目的仅供大家学习和交流,助力考生上岸!

3. 如果你想分享自己的自考经验或案例,可在后台编辑,经审核后发布在“中国自考网”,有下载币奖励哦!

4. 本站提供的课程资源,可能含有水印,介意者请勿下载!

5. 如有链接无法下载、失效或广告,请联系管理员处理(在线客服)!

6. 本站资源售价只是赞助,收取费用仅维持本站的日常运营所需!

7. 星光不问赶路人,岁月不负有心人,不忘初心,方得始终!

中国自考网 » 2022年4月自考10783数字系统设计与PLD应用技术试题(历年真题)